Cadence and TSMC Expand AI Silicon Design Collaboration for Faster, Efficient Tapeouts

April 22, 2026

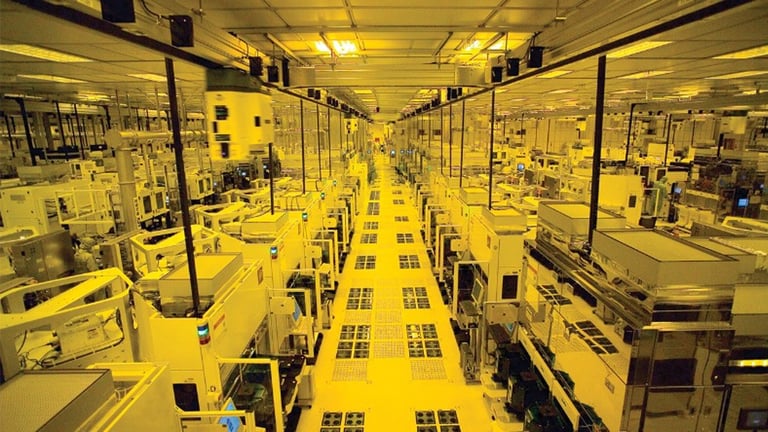

Cadence and TSMC are expanding collaboration to accelerate AI silicon design across TSMC N3, N2, A16, and A14 nodes, delivering IP, end-to-end design infrastructure, and certified flows to speed tapeouts.

Industry notes emphasize signoff-ready, cross-domain design flows for AI silicon and highlight collaboration among Cadence, TSMC, NVIDIA, Arm, and Positron.

Overall, joint efforts focus on AI-powered EDA tools and certified design enablement across leading-edge technologies to improve speed, accuracy, and design confidence for customers, with an emphasis on energy efficiency.

Calibre 3DStack and Calibre 3DThermal now support 3D IC design verification and thermal analysis for TSMC 3DFabric, including 3D interposer and antenna flows with certified 3D thermal verification for specified conditions.

Siemens’ mPower analog is certified for transistor-level EM/IR sign-off on N2P, while Aprisa for digital implementation carries N2P tool certification, signaling readiness for advanced-node workflows.

Cadence reported strong financials with double-digit revenue growth and high gross margins driven by its IP and software licensing business.

Cadence expanded AI partnerships with NVIDIA and Google, and received bullish price targets from Needham and KeyBanc following AI product announcements at CadenceLIVE 2026.

Industry voices from Arm and Positron praised the Cadence-TSMC collaboration for enabling faster, more confident tapeouts and high-speed interfaces.

Cadence’s broader strategy focuses on accelerating AI-enabled EDA workflows and chip design productivity through partnerships and new product releases.

Cadence platforms Genus, Innovus, and Cerebrus were enhanced to support DTCO, NanoFlex Pro architecture, and high-bandwidth interfaces like PCIe 6.0 SerDes, speeding convergence to tapeout-ready results.

Customer momentum is evident at 3nm and 2nm nodes, with multiple designs on TSMC’s latest technologies and Cadence-TSMC flows and IP gaining broad adoption; Positron licensed PCIe 6.0 SerDes IP for a second-generation AI accelerator.

Solido Design Environment supports reliability-aware verification in TSMC’s A14 CDRF flow, including aging, self-heating, and SOA checks, with variation-aware verification and automated cell optimization.

Summary based on 10 sources

Get a daily email with more AI stories

Sources

Investing.com • Apr 22, 2026

Cadence expands TSMC partnership for AI chip design tools

Siemens Digital Industries Software

Siemens & TSMC to advance AI for semiconductor design

Siemens Digital Industries Software

Siemens & TSMC to advance AI for semiconductor design

Siemens Digital Industries Software

Siemens & TSMC to advance AI for semiconductor design